Prodigy S8-40 Logic Systems

Prodigy S8-40ロジックシステムは、最新のAMD FPGAデバイスと、高性能なI/Oコネクタの使用により、今日のSoC設計において最高のパフォーマンスと最大のスケーラビリティを提供します。最新のコンパイル、ランタイム、デバッグソフトウェアスイートと共に使用することで、ユーザーは迅速にプロトタイプを立ち上げ、検証に於ける生産性を向上させることができます。

技術ハイライト

・最大40,000万ASICゲート相当の容量を提供します

・柔軟かつ拡張可能なI/Oアーキテクチャを備えています

・高い性能で革新的な検証に貢献します

・迅速なシステム立ち上げのための、強化されたツールチェーン

・豊富な種類のプロトタイプ用拡張ボードをご提供

| 推定ASICゲート数(100万) | 40 |

| FPGA Count | 1 |

| システム論理セル (K) | 7,352 |

| FPGA内部メモリ (Mb) | 891 |

| DSPスライス数 | 14,352 |

| 外部ユーザI/Os | 486 |

| GTYP(32.75Gbps) | 28 |

| GTM(58Gbps (112Gbps)) | 140 |

| CCIX & PCIe® w/DMA (CPM5) | 2 x Gen5x8, CCIX |

| PCIエクスプレス®、CXL搭載 | 2 x Gen4 |

| その他のコネクタ | APU(ARM Cortex-A72), RPU(ARM Cortex-R5F)4 |

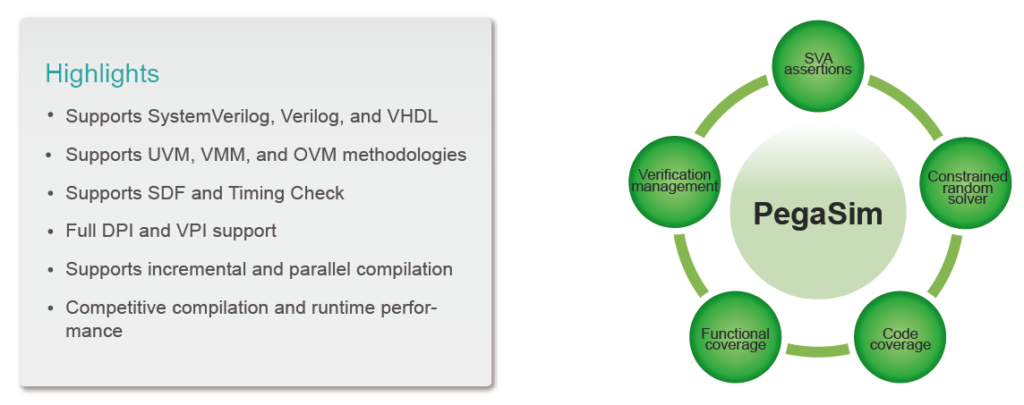

PegaSim

PegaSimはS2Cによって開発された高性能かつミックスドランゲージ対応のロジックシミュレータです。

PegaSimは革新的なアーキテクチャアルゴリズムを利用して、高性能シミュレーションと制約付きランダムソルバを実現します。

PegaSimはSystemVerilog、Verilog、VHDL、UVM方法論など、様々な設計・検証言語をサポートします。

主な特徴

複数の設計・検証言語をサポート

・Verilog (IEEE 1364)

・SystemVerilog (IEEE 1800-2017)

SVAアサーション、制約付きランダム・ソルバを、機能カバレッジ

DPIとVPIをフルサポート

・UVMメソドロジ(IEEE 1800.2)

UVM、VMM、OVMメソドロジをサポート

・VHDL言語 (IEEE 1076-1993)

std_logic_1164およびnumeric_stdなど

・IP暗号化をサポート (IEEE 1735)

クロスランゲージ(VHDL/SV)相互運用性

・SV内部でVHDLをインスタンス化可能。VHDLを任意の深さまでインスタンス化可能

・インスタンスはパラメータ/ジェネリックをオーバーライド可能

・ポート接続での適切な型変換

容易な導入と使用

・クラウド展開とクラウド上での回帰タスクの並列実行をサポート

・波形解析やソースコード・デバッグを柔軟にサポートする自社開発波形フォーマット及び業界基準の波形フォーマットをサポート

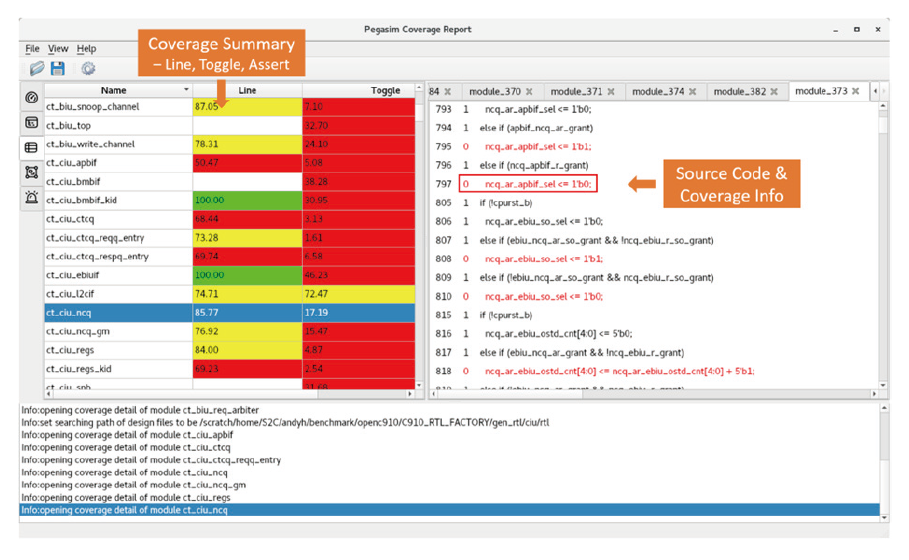

コードカバレッジ

・行/ブロック、トグル、式のカバレッジ解析をサポート

・アサーション・カバレッジ分析をサポート

複数のシミュレーション技術をサポート

・インクリメンタルおよび並列コンパイル

・SDFとタイミング・チェックをサポート

・エミュレーションおよびプロトタイピング・システムとのコ・シミュレーション

ミックスドランゲージ対応

・VHDL、Verilog、SystemVerilog混在シミュレーション

・数億ゲートに及ぶ大規模設計シミュレーション

・コンパイルとランタイムの性能は、業界をリードする商用シミュレータに匹敵する性能を実現

カバレッジ解析

チップ検証のプロセスでは、RTLコードのカバレッジを解析することで、検証の完全性を測定することができます。

PegaSimにはカバレッジ解析ツールが統合されており、高度なカバレッジ主導の検証手法をサポートしています。

カバレッジ目標を定義、測定、報告し、カバレッジホールを見つけることができます。